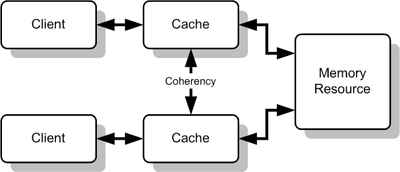

Um cache pode ser usado para melhorar o desempenho do acesso a um determinado recurso. Quando existem vários caches desse tipo para o mesmo recurso, como mostrado na figura, isso pode levar a problemas. A coerência do cache ou Cache coherency refere-se a uma série de maneiras de garantir que todos os caches do recurso tenham os mesmos dados, e que os dados nos caches façam sentido (chamados de integridade de dados). A coerência do Cache é um caso especial de coerência da memória.

Pode haver problemas se houver muitos caches de um recurso de memória comum, pois os dados no cache podem não fazer mais sentido, ou um cache pode não ter mais os mesmos dados que os outros. Um caso comum onde o problema ocorre é o cache de CPUs em um sistema de multiprocessamento. Como pode ser visto na figura, se o cliente superior tem uma cópia de um bloco de memória de uma leitura anterior e o cliente inferior muda esse bloco de memória, o cliente superior poderia ficar com um cache de memória inválido, sem saber. A coerência do cache existe para gerenciar tais conflitos e manter a coerência entre cache e memória.