Desenvolvimento: 1989–2000

Em 1989, a HP pensou que as arquiteturas do Reduced InstructionSet Computing (RISC) estavam presas a uma instrução por ciclo. Os pesquisadores da HP tentaram criar um novo tipo de arquitetura de processador, mais tarde chamado Explicitly Parallel Instruction Computing (EPIC), que permite ao processador usar muitas instruções em cada ciclo do relógio. O EPIC usa uma forma de arquitetura de instruções muito longa (VLIW), na qual 1 palavra de instrução tinha muitas instruções. Com o EPIC, o compilador verifica quais instruções podem ser usadas ao mesmo tempo, para que o processador possa executar as instruções sem precisar de métodos complicados para ver quais instruções usar ao mesmo tempo. O objetivo desta idéia é permitir uma melhor inspeção do código no momento da compilação para verificar oportunidades adicionais para múltiplas execuções ao mesmo tempo, e simplificar o projeto do processador e economizar eletricidade, eliminando a necessidade de instruções de programação de tempo de execução.

A HP achou que não era bom para empresas individuais de sistemas empresariais como a HP fazer processadores proprietários, então a HP trabalhou com a Intel em 1994 para criar a arquitetura IA-64, feita com as idéias do EPIC. A Intel queria fazer um grande esforço na criação da IA-64 na expectativa de que o processador resultante fosse usado pela maioria dos sistemas empresariais. A HP e a Intel tiveram um grande esforço de projeto para fazer o primeiro produto Itanium, Merced, em 1998.

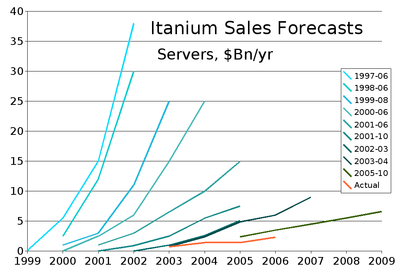

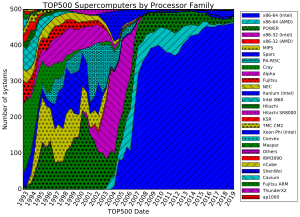

Durante a criação, a Intel, HP e outros analistas do setor pensaram que a IA-64 seria muito popular em servidores, estações de trabalho e desktops, e um dia substituiria as arquiteturas RISC e Complex Instruction Set Computing (CISC) para aplicações multiuso. A Compaq e a Silicon Graphics deixaram de trabalhar em suas arquiteturas Alpha e MIPS para passar para a arquitetura Itanium.

Muitos grupos criaram sistemas operacionais para Itanium, incluindo Microsoft Windows, OpenVMS, Linux e tipos UNIX como HP-UX, Solaris, Tru64 UNIX e Monterey/64 (os três últimos nunca terminaram de trabalhar com o Itanium). Em 1997, muitos descobriram que a arquitetura Itanium e o compilador eram mais difíceis de usar do que eles pensavam. Questões tecnológicas como a contagem muito alta de transistores necessários para as grandes palavras de instrução e as grandes caches. [] Houve também problemas com o projeto, pois as duas partes da equipe utilizavam métodos diferentes e tinham prioridades ligeiramente diferentes. [] Como Merced foi o primeiro processador EPIC, sua criação teve mais problemas do que a equipe havia pensado. Além disso, o conceito EPIC requer habilidades de compilação diferentes que nunca tinham sido criadas antes, portanto, era necessário mais pesquisa. []

A Intel anunciou o nome do processador, Itanium, em 4 de outubro de 1999. Em apenas algumas horas, o nome Itanic havia sido usado como piada, (uma referência ao Titanic, o navio "insubmersível" que afundou em 1912 ("Itanium + Titanic = Itanic")). "Itanic" também foi usado pelo The Register, e outros, para dizer que o investimento multibilionário no Itanium, e a demanda inicial com ele, não significaria nada porque eles pensavam que o Itanium iria falhar.

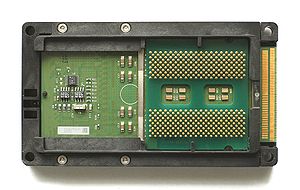

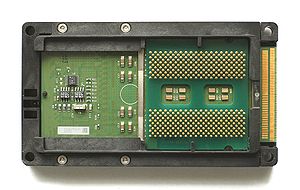

Itanium (Merced): 2001

| Itanium (Merced) |

|

|

| Produzido em | De junho de 2001 a junho de 2002 |

| Fabricante(es) comum(s) | |

| Máx. Taxa de relógio da CPU | 733 MHz a 800 MHz |

| Velocidades da FSB | 266 MT/s |

| Conjunto de instruções | Itanium |

| Número de núcleos | 1 |

| Cache L2 | 96 KB |

| Cache L3 | 2 ou 4 MB |

| Tomada(s) | |

| Nome(s) central(is) | |

Quando o Itanium foi lançado em junho de 2001, seu desempenho não era superior ao dos processadores concorrentes RISC e CISC. A Itanium competia com sistemas de baixa potência (principalmente 4-CPU e sistemas pequenos) com servidores baseados em processadores x86, e com alta potência, como a arquitetura POWER da IBM e a arquitetura SPARC da Sun Microsystems. A Intel mudou o Itanium para trabalhar com o negócio de alta potência e computação HPC, tentando copiar o mercado de sucesso do x86 (ou seja, 1 arquitetura, muitos fornecedores de sistemas). O sucesso da primeira versão do processador foi apenas com a substituição do PA-RISC em sistemas HP, Alpha em sistemas Compaq e MIPS em sistemas SGI, mas a IBM também fez um supercomputador baseado nesta arquitetura. POWER e SPARC eram fortes, e a arquitetura x86 cresceu mais no espaço empresarial, por causa da escala mais fácil e da base de instalação muito grande.

Apenas alguns milhares de sistemas usando o 1º processador Itanium, Merced, foram vendidos, devido ao desempenho mais fraco, alto custo e menos software Itanium. A Intel viu que o Itanium exigia mais software nativo para funcionar bem, então a Intel fez milhares de sistemas para fornecedores de software independentes para ajudá-los a fazer o software Itanium. A HP e a Intel trouxeram o 2º processador Itanium, Itanium 2, para o mercado um ano depois.

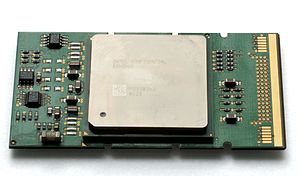

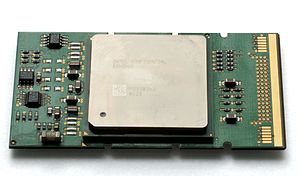

Itanium 2: 2002-2010

| Itanium 2 (McKinley) |

|

|

| Produzido em | De 2002 a 2010 |

| Projetado por | Intel |

| Fabricante(es) comum(s) | |

| Máx. Taxa de relógio da CPU | 900 MHz a 2,53 GHz |

| Conjunto de instruções | Itanium |

| Número de núcleos | 1, 2, 4 ou 8 |

| Cache L2 | 256 KB em Itanium2

256 KB (D) + 1 MB(I) ou 512 KB (I) em (Itanium2 série 9x00) |

| Cache L3 | 1,5-32 MB |

| Tomada(s) | - PAC611

- FC-LGA6 (LGA1248) (série Itanium 9300)

|

| Nome(s) central(is) | - McKinley

- Madison

- Hondo

- Deerfield

- Montecito

- Montvale

- Tukwila

- Poulson

|

O processador Itanium 2 foi lançado em 2002, para servidores empresariais e não para todos os computadores de alta potência. A 1ª versão do Itanium 2, codinome McKinley, foi criada pela HP e Intel. Ela corrigiu muitos dos problemas do 1º processador Itanium, que foram causados principalmente por um subsistema de memória ruim. McKinley tinha 221 milhões de transistores (25 milhões deles eram para lógica), e era 19,5 mm por 21,6 mm (421 mm2) e foi criado com um processo de design de 180 nm, e um processo CMOS com 6 camadas de alumínio.

Em 2003, a AMD lançou o Opteron, que implementou a primeira arquitetura x86-64 (chamada AMD64 na época). Opteron foi muito mais bem-sucedido porque foi uma atualização fácil do x86. A Intel implementou o x86-64 em seus processadores Xeon em 2004.

A Intel lançou um novo processador Itanium 2, com o nome de código Madison, em 2003. Madison usou um processo de 130 nm e foi a base de todos os novos processadores de Itanium até junho de 2006.

Em março de 2005, a Intel anunciou que estava trabalhando em um novo processador Itanium, codinome Tukwila, a ser lançado em 2007. O Tukwila teria 4 núcleos de processador e substituiria o barramento Itanium por uma nova Interface de Sistema Comum, que também seria usada por um novo processador Xeon. Mais tarde naquele ano, a Intel mudou a data de lançamento do Tukwila para o final de 2008.

Em novembro de 2005, os maiores fabricantes de servidores Itanium trabalharam com a Intel e muitos fornecedores de software para criar a Itanium Solutions Alliance, para promover a arquitetura e acelerar a portabilidade do software. A Aliança diz que seus membros investiriam 10 bilhões de dólares em soluções Itanium até o final da década.

Em 2006, a Intel entregou o Montecito (comercializado como a série Itanium 2 9000), um processador de 2 núcleos que tinha aproximadamente 2x de desempenho e 20% menos consumo de energia.

A Intel lançou a série Itanium 2 9100, codinome Montvale, em novembro de 2007. Em maio de 2009, o lançamento do Tukwila, sucessor de Montvale, foi alterado novamente, com o lançamento para OEMs previsto para o primeiro trimestre de 2010.

Itanium 9300 (Tukwila): 2010

O processador Itanium 9300 series, codinome Tukwila, foi lançado em 8 de fevereiro de 2010, com maior desempenho e quantidade de memória.

Tukwila utiliza um processo de 65 nm, tem entre dois e quatro núcleos, até 24 MB de cache de CPU, tecnologia Hyper-Threading e novos controladores de memória. Possui também correção de dados em dois dispositivos, o que ajuda a resolver problemas de memória. Tukwila também tem o Intel QuickPath Interconnect (QPI) para substituir a arquitetura de barramento Itanium. Ele tem uma largura de banda máxima do processador interno de 96 GB/s e uma largura de banda máxima de memória de 34 GB/s. Com QuickPath, o processador tem controladores de memória incorporados, que controlam a memória usando interfaces QPI para se comunicar com outros processadores e hubs de E/S. O QuickPath também é usado com processadores Intel usando a arquitetura Nehalem, para que o Tukwila e o Nehalem possam usar os mesmos chipsets. O Tukwila incorpora quatro controladores de memória, cada um dos quais suporta vários DIMMs DDR3 através de um controlador de memória separado, semelhante ao processador Nehalem Xeon com o nome de código Beckton.

Itanium 9500 (Poulson): 2012

| | Este artigo precisa ser atualizado. Você pode ajudar a Wikipédia atualizando-o. (março de 2014) |

O processador Itanium série 9500, com o nome de código Poulson, é o processador seguinte ao Tukwila e foi lançado em 8 de novembro de 2012. A Intel diz que ele salta a tecnologia de processo de 45 nm e utiliza a tecnologia de processo de 32 nm; ele apresenta 8 núcleos, tem uma arquitetura de 12 núcleos, adições multi-tarefas e novas instruções para o paralelismo, incluindo a virtualização. O tamanho do cache Poulson L3 é de 32 MB. O tamanho do cache L2 é de 6 MB, 512 I KB, 256 D KB por núcleo. O tamanho do Poulson é 544 mm², menor que o tamanho do Tukwila (698,75 mm²).

No ISSCC 2011, a Intel apresentou um documento chamado "A 32nm 3,1 bilhões de Transistor 12-Wide-Issue Itanium Processor for Mission Critical Servers". Dada a história da Intel de compartilhar detalhes sobre microprocessadores Itanium no ISSCC, este trabalho provavelmente se refere a Poulson. O analista David Kanter especula que Poulson usará uma nova arquitetura, com uma forma mais avançada de multi-tarefa que usa até duas roscas, para melhorar o desempenho para trabalhos com uma única rosca e multi-tarefa. Novas informações foram divulgadas na conferência Hot Chips.

As novas informações reclamam melhorias em multithreading, melhorias de confiabilidade (Instruction Replay RAS) e algumas novas instruções (prioridade de thread, instruções inteiras, pré-venda de cache, dicas de acesso aos dados).

Na Notificação de Mudança de Produto (PCN) 111456-01 da Intel, foram listados 4 modelos de CPU Itanium série 9500, que foram removidos em uma versão revisada do documento. As peças foram listadas mais tarde no banco de dados de folhas de dados de Declaração de Material (MDDS) da Intel. A Intel publicou mais tarde o manual de referência do Itanium 9500.

Os modelos são:

| Número do processador | Freqüência |

| 9520 | 1,73 GHz |

| 9540 | 2,13 GHz |

| 9550 | 2,4 GHz |

| 9560 | 2,53 GHz |